内含CPU所有Verilog源码、论文详细解析,作业成绩为优秀 所有代码和论文皆为原创,严禁二次转载!

”计算机组成原理 RISC-V 计算机组成原理大作业 单周期CPU设计“ 的搜索结果

计算机组成原理综合实验,计算机组成原理期末大作业,设计完成了35条RISC-V指令,完成了单周期CPU的设计,开发工具采用Vivado、语言采用Verilog HDL、FPGA采用PYNQ访问PYNQ云平台使用。

MIPS指令译码器设计|定长指令周期---时序发生器FSM设计|定长指令周期---时序发生器输出函数设计|硬布线控制器组合逻辑单元|定长指令周期---硬布线控制器设计|定长指令周期---单总线CPU设计 学习交流q2267261634

头歌educoder教学实践平台计算机组成原理单总线CPU设计(定长指令周期3级时序)(HUST)。第1关—第6关,源代码txt格式。 第1关 MIPS指令译码器设计 第2关 定长指令周期---时序发生器FSM设计 第3关 定长指令周期---时序...

单周期cpu的设计-37条指令-trace比对版,完整的.v文件。不过还是建议去看我写的文章https://blog.csdn.net/qq_52399968/article/details/125843005

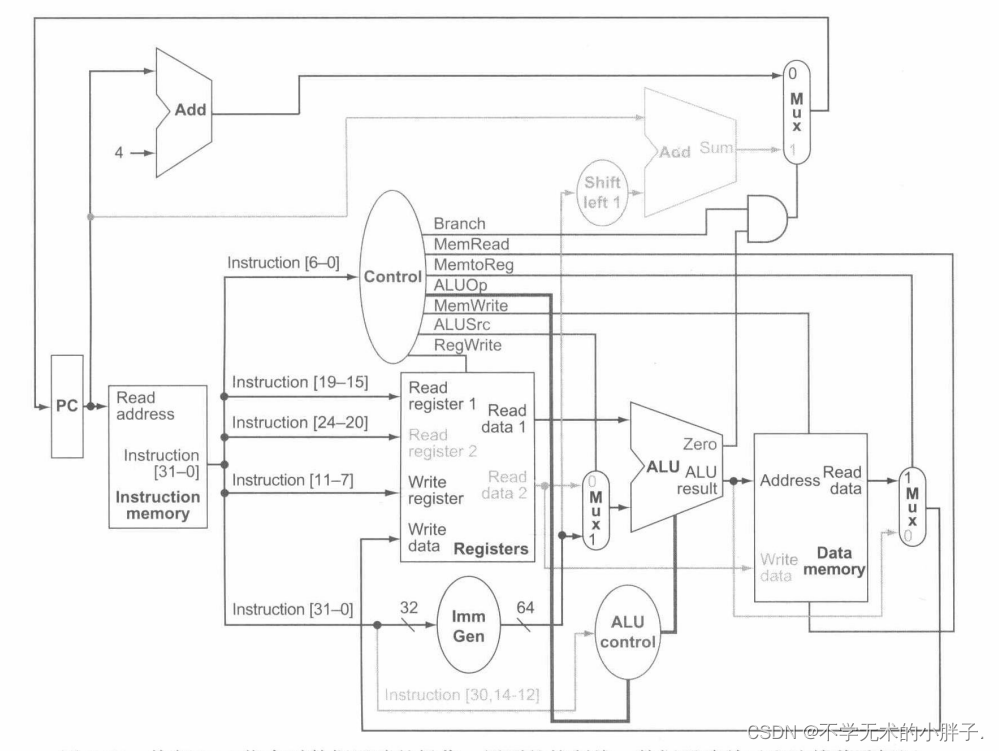

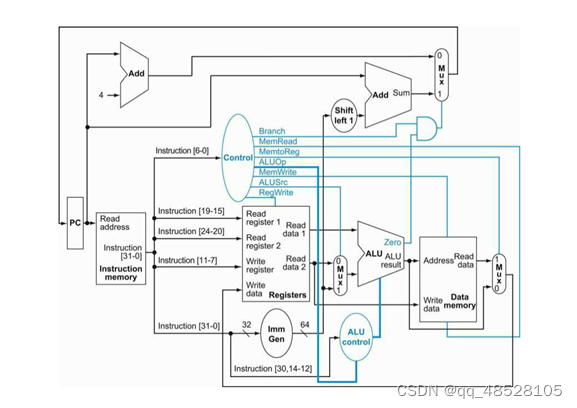

本文采用RISC-V架构设计CPU,实现单周期CPU,设计取指、译码、执行、访存、写回五个阶段,扩展实现了RV32I指令集,通过该指令集所有指令的仿真测试。工具采用了iverilog和GTKwave。(具体仿真调试过程见下一篇文章)

本实训项目帮助学生理解定长指令周期三级时序系统的设计,能利用该时序构造硬布线控制器,支持5条典型MIPS指令在单总线CPU上运行,最终CPU能运行内存冒泡排序。 第1关MIPS指令译码器设计 第2关定长指令周期---时序...

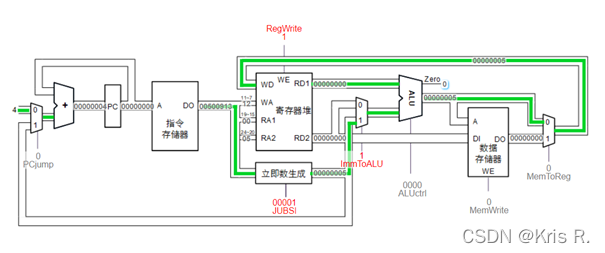

立即数imm由立即数生成模块生成,根据I型运算类指令的指令格式,I型立即数的低12位imm[11:0]来自指令的31~20位,按照符号位扩展方法扩展得到32位立即数送给ALU, ALU完成具体的运算,运算的结果通过寄存器堆的数据写...

中山大学数据科学与计算机学院计算机组成原理实验作业代码

对于 RISC-V 架构,本文实现了一种基于此架构的 45 条指令单周期非流水线 的 CPU。实现方式是事先设计好指令所需的组件、各类控制信号的取值、各类指 令的数据通路,然后基于 Vivado2018.3 用 Verilog 语言进行硬件...

RISC-V Assembly 插件撰写代码: 具体代码如下: 翻译成十六进制指令: 将上述代码翻译成十六进制指令,并初始化指令寄存器: 初始化存储器: 行为仿真测试: 其中 result 结果为 2,结果正确。 各部件连线图: ...

完整目录 完整代码和论文 心得体会 组员一: 这次实验花了许多时间,小组也一起熬了很多夜,主要还是因为要从头开始 学一些东西,比如 Verilog 编程,Vivado 封装...经过本次实验,然我进一步理解了 RISC-V 架构的 CPU

RISC-V模型机的目标指令集、RISC-V模型机的部件设计、运算及传送指令的数据通路设计、访存指令的数据通路设计、转移类指令的数据通路设计、RISC-V模型机控制单元CU的有限状态机设计

1 MIPS指令译码器设计 2 定长指令周期---时序发生器FSM设计 3 定长指令周期---时序发生器输出函数设计 4 硬布线控制器组合逻辑...6 定长指令周期---单总线CPU设计 全通关(放入logisim可查看电路,改成txt可上传代码)

该实验用Vivado 2018.3 进行Verilog代码编写、TestBench代码编写(其实也可以使用...0x02设计数据通路 难点在于多选器的使用: 0x03项目整体代码及说明 https://github.com/rave1sking/single_cycle_RISCV_CPU_Desig

摆烂才是王道

1.组合逻辑设计CU的外特性如下所示机器主频时钟,输入到节拍发生器,产生节拍序列输入到CU中控制各种微操作IR指令寄存器操作码输入到操作码译码中产生各种控制信号来控制完成各种操作1.1微操作节拍安排假设CPU内部...

推荐文章

- c语言链表查找成绩不及格,【查找链表面试题】面试问题:C语言学生成绩… - 看准网...-程序员宅基地

- 计算机网络:20 网络应用需求_应用对网络需求-程序员宅基地

- BEVFusion论文解读-程序员宅基地

- multisim怎么设置晶体管rbe_山东大学 模电实验 实验一:单极放大器 - 图文 --程序员宅基地

- 华为OD机试真题-灰度图恢复-2023年OD统一考试(C卷)-程序员宅基地

- 【机器学习】(周志华--西瓜书) 真正例率(TPR)、假正例率(FPR)与查准率(P)、查全率(R)_真正例率和假正例率,查准率,查全率,概念,区别,联系-程序员宅基地

- Python Django 版本对应表以及Mysql对应版本_django版本和mysql对应关系-程序员宅基地

- Maven的pom.xml文件结构之基本配置packaging和多模块聚合结构_pom <packaging>-程序员宅基地

- Composer 原理(二) -- 小丑_composer repositories-程序员宅基地

- W5500+F4官网TCPClient代码出现IP读取有问题,乱码问题_w5500 ping 网络助手 乱码 send(sock_tcps,tcp_server_buff,-程序员宅基地